这学期的《材料科学基础》课程考核要求每人讲述一个与材料科学相关的故事,今日轮到我,遂将口述原文记录于此,附PPT图片。

P1

(封面页)

P2

P3

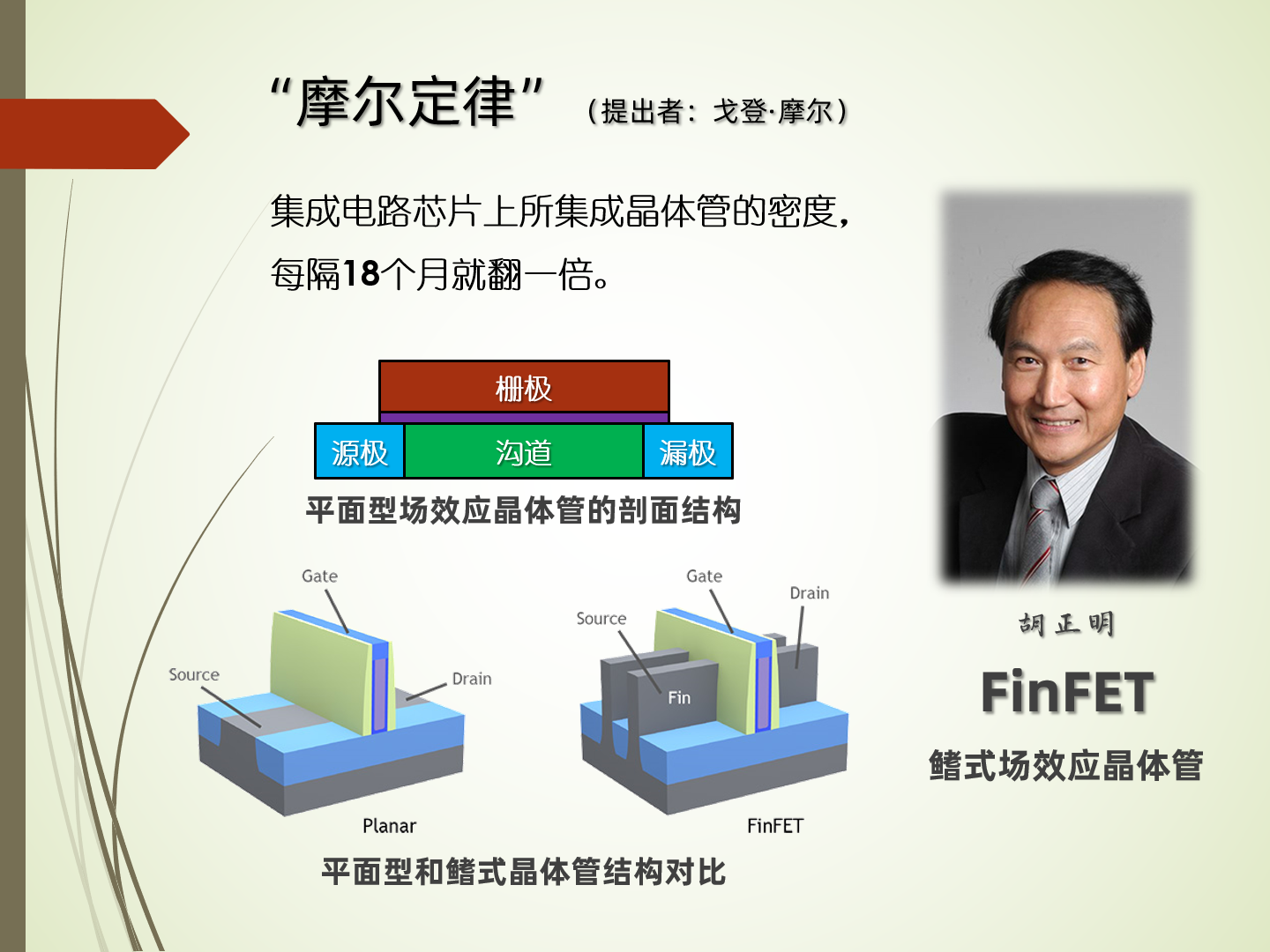

在芯片制造领域,有一个非常经典的“摩尔定律”,它说“集成电路芯片上所集成晶体管的密度,每隔18个月就翻一倍”。首先,这个“摩尔定律”并不是一个物理定律,而是上世纪60年代intel创始人之一——戈登·摩尔根据经验提出的一个预测。

半导体芯片发展了这么多年,早期确实是按照这个所谓摩尔定律在稳步向前的,但是28nm之后,因为短沟道效应的影响,传统的平面型晶体管工艺就达到极限了,好在胡正明先生发明的FinFET技术,也就是前面视频提到的鳍式场效应晶体管,让硅基芯片的晶体管密度还能继续提高。

这里的鳍式场效应晶体管可以理解为,把传统的平面型晶体管给做出了立体结构,让源极、漏极和沟道凸了起来,做成了一个Fin(鳍片)的形状,嵌到栅极里面去,减小了沟道电阻,同时减小了单个晶体管的占地面积,所以可以进一步提高晶体管密度。

P4

然而,现在FinFET技术也坚持不下去了。很直观的表现就是,去年下半年发布的一批5nm手机SOC,包括麒麟9000、苹果A14、骁龙888在内,功耗控制无一例外全部翻车,翻车最严重的就是骁龙888,因为它用的是三星的5nm工艺,虽然也叫5nm,但三星的这个5nm工艺比较差,晶体管密度只有1.27亿个每平方毫米,而台积电5nm工艺的晶体管密度是1.71亿个每平方毫米。另外,去年NVIDIA发布的RTX30系列安培架构显卡,用的是三星8nm工艺,相比于上一代RTX20系列图灵架构显卡,功耗也涨得离谱,RTX3090峰值功耗可以冲到500W,堪称核弹。

上个月有供应链消息说台积电的3nm工艺已经开始风险量产,预计下半年可以正式投产,反观intel,10nm工艺的产品去年才开始出货,还仅仅用在了移动端低压芯片上,也就是11代低压酷睿Tigerlake-U,同代标压芯片,也就是今年2月份发布的11代桌面级酷睿,还在用14nm+++…工艺,并且能耗比还不如上一代,10nm工艺的桌面级产品最早也要等到今年年底的12代酷睿。

了解了这么多令人迷惑的现象,我们不禁要想——这个摩尔定律是不是已经失效了啊?

做出判断之前,我们要先来看看下面这两个问题——

P5

第一个问题:如今的“xx nm”工艺还能否真实反映晶体管密度?

第二个问题:各大芯片制造商的同名“xx nm”工艺有多少区别?

先看一张表。

从这张表的数据里我们看到,intel、台积电、三星三家厂商同样被叫作“10nm”的工艺,它们的晶体管密度居然相差这么大。

我们再看看上个月底Anandtech主编Ian Cutress的爆料,可以发现,intel这个距离量产还遥遥无期的7nm工艺,晶体管密度不但超过台积电5nm工艺,甚至接近了台积电3nm工艺。

P6

我们再来专门看看近些年台积电TSMC的制程发展。这里的N几就代表了几nm工艺,N7P是指7nm DUV工艺,就是用193nm波长的深紫外光来进行光刻,N7+是指7nm EUV工艺,就是用13.5nm波长的极紫外光来进行光刻。

7nm DUV和7nm EUV虽然通称7nm工艺,但是7nm EUV可以一次曝光搞定,而不需要多重曝光,所以效率更高、良品率也更高,还能更极限地去堆晶体管密度。这里的N6就是由7nm EUV进一步优化出来的。后面在鳍片里面掺点高电子迁移率的锗,再把导线材料改成钴和钌,整出来个N5,N5再优化优化出来个N5P,然后再强行优化优化,N3又出来了。台积电后面还想搞2nm、1nm,但是会放弃FinFET,改用一种叫GAA-FET的新技术,Gate-All-Around FET,全环绕栅极场效应晶体管。三星也已经决定在3nm工艺节点用上GAA-FET。

但是按照一般理解,硅晶体管的栅极长度低于5nm,就会产生一种叫量子隧穿的物理现象,造成电子失控、晶体管漏电,栅极就没法控制晶体管的通断了,晶体管也就没用了,然而他们是怎么做到这么小的呢?

实际上他们并没有把栅极和沟道的长度真的做到这么小。自从引入FinFET技术以后,各家宣传的几nm几nm工艺已经变成了一个营销代号,而不能代表真实的栅极和沟道长度了。如果我们严谨地从晶体管密度来看的话,所谓的“摩尔定律”早已失效。从传统的平面型MOSFET,到3D的FinFET,再到3D堆叠的GAAFET,工艺流程越来越繁琐,造出来的晶体管在量子隧穿的边缘疯狂试探,硅基芯片堆晶体管密度的潜力已经快被榨干了。接下来很长一段时间,芯片性能的提升或许只能更多地依靠芯片设计厂商的架构优化能力了。

当然,芯片设计厂商也确实在努力,去年NVIDIA发布的安培架构显卡、AMD发布的Zen3架构CPU和RDNA2架构显卡,都有着近几年来最大的性能提升,苹果公司也开创性地发布了首个ARM架构的电脑SOC,也就是M1,ARM公司前段时间也更新了已经10年没有更新的指令集Arm v9,intel终于也要在年底迎来一次巨大的架构改进,也就是所谓的“大小核架构”。此外,旨在实现芯片模块化的Chiplet技术和相关的先进封装工艺也正趋于成熟。

以上这些,我们可以欣慰地发现,至少在近几年,人类的计算机性能发展并不会因为摩尔定律的失效而产生太严重的瓶颈,但是,再远一点的未来呢?芯片架构再怎么优化,到后面也会越来越难,也难免会产生瓶颈。所以人类必须赶快找到一种新的材料来代替传统的硅基芯片,甚至需要寻找一种新形态的计算机,来代替通用计算机、代替冯·诺依曼架构计算机。我们今天不讨论量子计算、生物计算甚至类脑计算这些新形态的计算机,就讨论讨论那些有很大希望成为下一代芯片材料的东西。

P7

前面提到,台积电已经在5nm节点引入了锗、钴、钌这些新材料,实际上这是一个比较将就的思路,但也是目前研发和量产成本最低的思路。

我们先不改变硅基底,在此基础上把原先的二氧化硅绝缘层改成六方氮化硼。六方氮化硼的绝缘性能很好,可以做到0.7nm的厚度,同时保证绝缘性。去年台积电联合台湾交通大学做出了这种0.7nm厚的氮化硼绝缘材料,有希望利用这种材料开发1nm制程的芯片。

这篇Article发表在去年3月的《Nature》杂志上。这是他们的做法。

……(解释图)

我们注意到,这项研究的最后,作者提到了“单层MoS2场效应晶体管”这么一个东西,所以,我们接下来就看看这种可以用作晶体管核心部件,也就是沟道的新材料,层状二硫化钼。

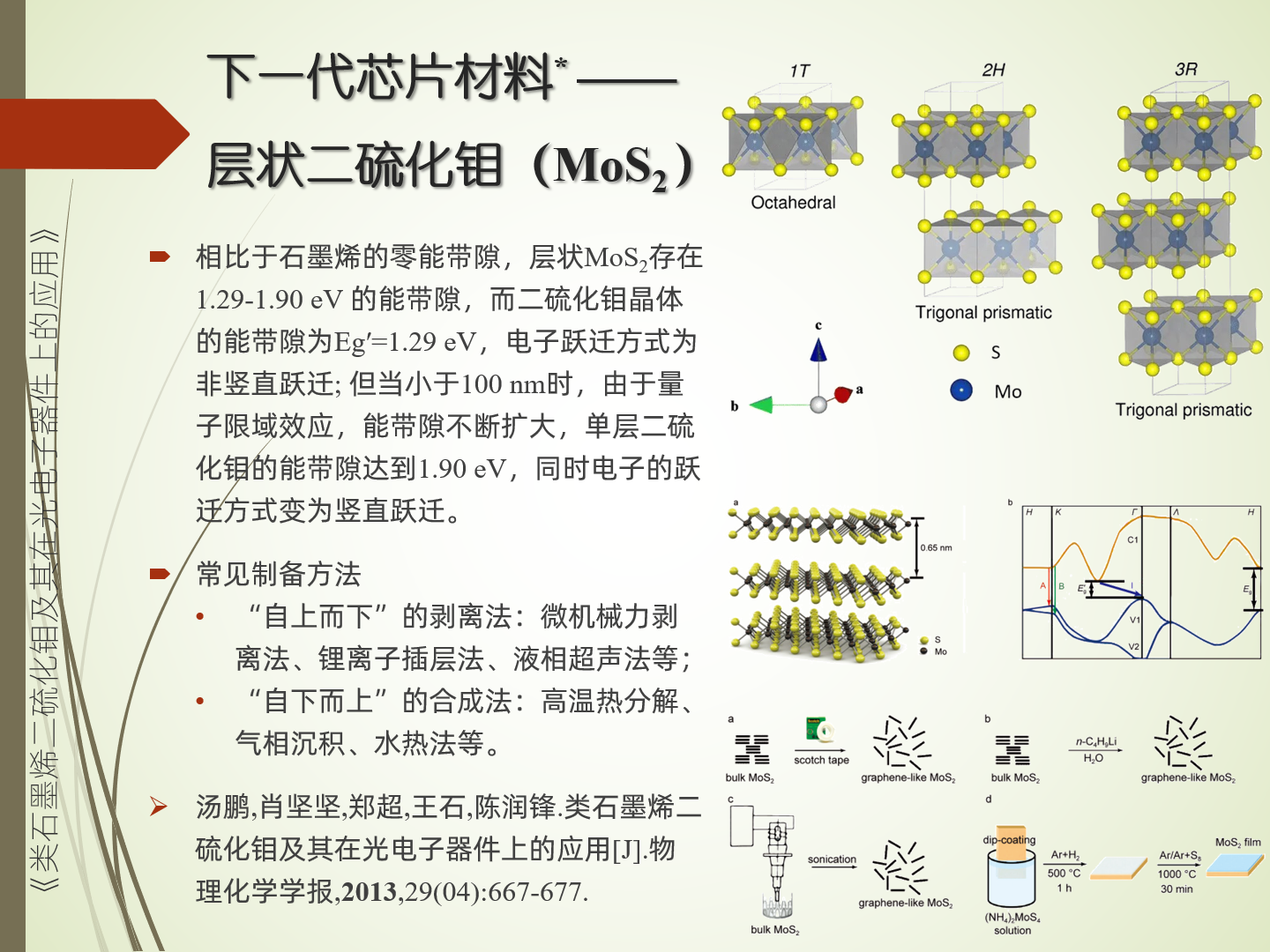

P8

顾名思义,层状二硫化钼具有层状结构,这一点和石墨烯相似,但和石墨烯的零能带隙不一样的是,层状二硫化钼存在1.29-1.90eV的能带隙,当它的层数堆得非常多,也就是宏观呈现块状的时候,能带隙是1.29eV,而当厚度减小到纳米级别的时候,因为量子限域效应,这个能带隙会随着层数的减少而变大,单层二硫化钼的能带隙达到1.90eV。这种特性就让它很适合用来做晶体管。

……(解释图)

P9

2016年,Science报道了劳伦斯伯克利实验室的研究成果:栅极长度仅1nm的二硫化钼晶体管,这也是如今世界上最小的晶体管。

从图中可以看到,这个晶体管用两层二硫化钼作为沟道材料,一根包裹在二氧化锆里面的单壁碳纳米管SWCNT作为栅极Gate的材料。

这是这个晶体管截止状态和饱和状态的电气特性示意图。

这个晶体管的设计非常巧妙。但是有一个很大的问题——这玩意怎么量产?如何同时做几百亿个到晶圆上去?

P10

时间关系,还有许多关于二硫化钼芯片的研究,就不一一介绍了,这里放一些有代表性的参考文献。

总之,为了芯片性能可以不断提升下去,人类还在一点点探索未来的芯片材料。我们应该保持乐观的态度,积极探索,风雨无阻向前进,相信摩尔定律还能延续,人类可以拥有美好的未来。

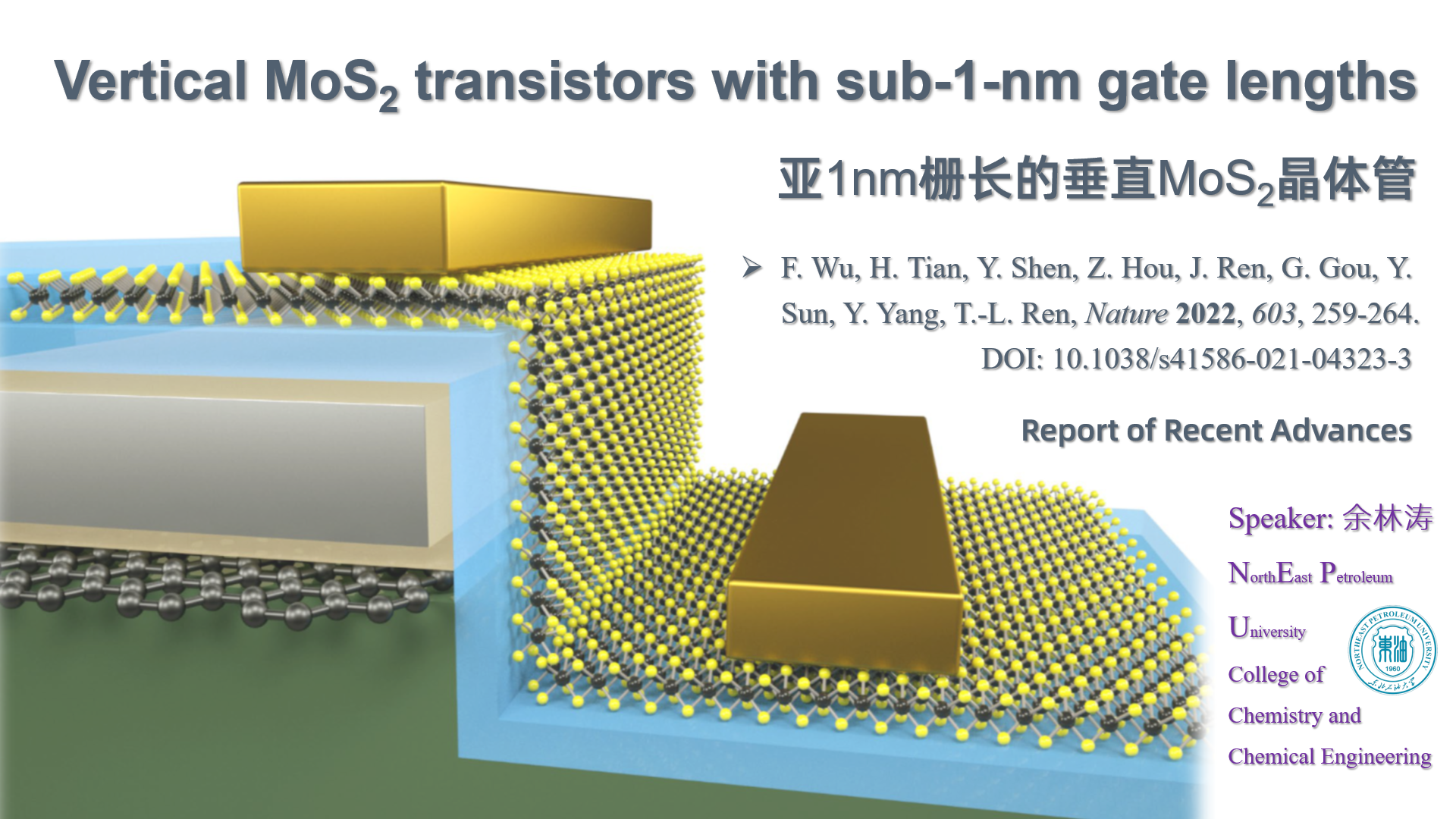

2022-04-18更新:今天出了个续集,因为最近看到清华的田禾团队在Nature发表了栅长0.34nm的晶体管。这次是在线上上课时讲的,录制下来了,此处直接放视频:

文章评论